оƬ��ُ�W(w��ng)��ע�����χ���(n��i)���ڙ�(qu��n)IC�����̬F(xi��n)؛�YԴ��оƬ��挍(sh��)�r��ԃ���ИI(y��)�r���������ُ����ICоƬ������(n��i)���I(y��)оƬ��ُƽ�_��

����

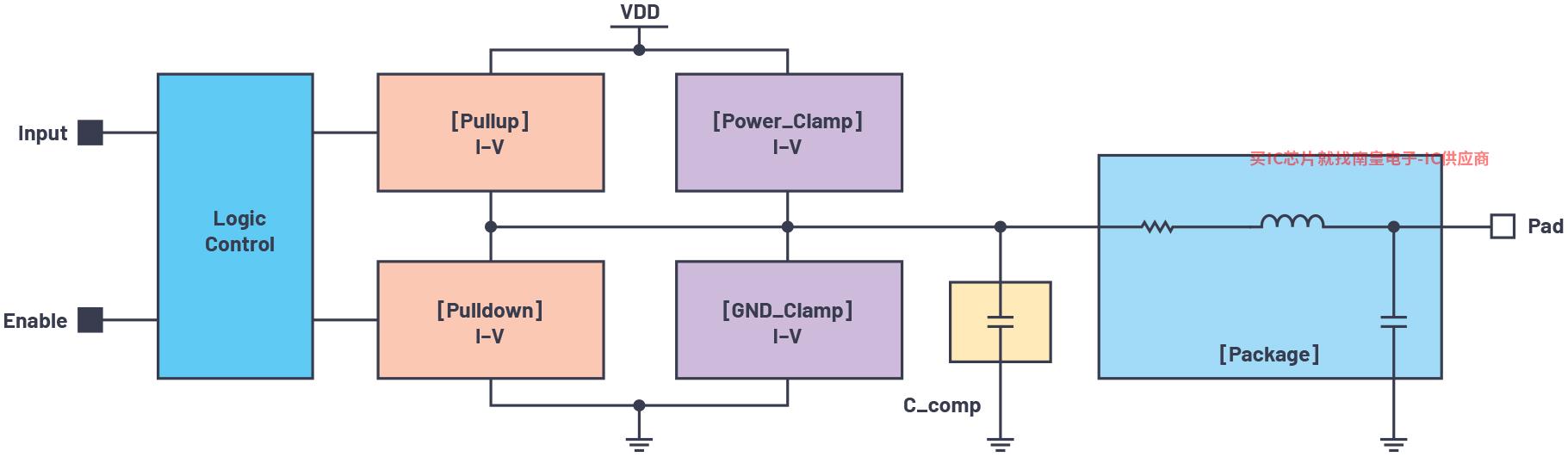

ģ�M�ژ�(g��u)���κ�ϵ�y(t��ng)�r�������P(gu��n)�I���á��������O(sh��)Ӌ���A(y��)�y���}��Ȼ�����ĕr�Ͱ��F���ġ��҂���Ŀ��(bi��o)����һ���Գɹ�����ģ�M���ٔ�(sh��)�ֽӿڕr������O(sh��)Ӌ����(d��ng)�ͺ���PCB�Ӿ����ܕ�Ӱ���̖�|(zh��)����IBISģ�����ڱ�ʾ�O(sh��)��Ĕ�(sh��)�ֽӿڡ�

��IBIS��ϵ�����µĵ�һ���֣�IBIS�Ա�����ʽ�г��������늉���һ�N�О�ģ��(I-V)�Լ�늉��͕r�g(V-T)��(sh��)��(j��)�������O(sh��)�䔵(sh��)�ֽӿڵ�늚����ԡ�IBISģ�͑�(y��ng)�M���ܜ�(zh��n)�_���o�����e�`���Ա����Ժ�ʹ�Õr���F(xi��n)���}�����⣬��(sh��)�ֽӿڵ�ÿ���������O(sh��)�䶼��(y��ng)�ṩ������IBISģ�͡���(d��ng)�͑���Ҫ�r������ֱ�ӏ������̵ľW(w��ng)������d������(sh��)���ǿ�����ˡ�����IBISģ���Ñ���(j��ng)�������Ć��}֮һ��ģ�͵Ŀ����ԡ���(d��ng)�������O(sh��)Ӌ���x��IJ����]�ЕrIBIS��ģ���У���a(ch��n)Ʒ�_�l(f��)���ܕ����衣

IBISԓģ����������������ṩ�����Ñ�Ҳ���Ԅ�(chu��ng)��IBISģ�͡����Ľ�B�����ʹ�á�LTspice������SPICE��(chu��ng)���������ģ��IBISģ�͡�������IBIS��ģ�փԣ�IBIS 4.��B0��)�е�Ҏ(gu��)��LTspiceģ�M�O(sh��)�á�߀��B�����ʹ�ö��ԺͶ����|(zh��)�������(y��n)�CIBISģ�͡�

ʲô���������IBISģ�ͣ�

�����͑�ʹ��LTspice��(chu��ng)��������IBISģ����Ҫ�ȶ��x����һ�~��������IBISģ�Ͳ��Hȡ�Q��I/Oģ���P(gu��n)�I��Ҳȡ�Q����Ҫ��ģ�Ĕ�(sh��)�־��_������͡��@��ζ����Ҫ����ҕIBIS���ڰ汾���x�˾��_ģ�͵����Ҫ��ͮ�(d��ng)�r��ģ�Ĕ�(sh��)�ֽӿ���͡���(sh��)�C�����ζ�CMOS��ʹ�þ��_��IBIS��ģ��εĔ�(sh��)��IOһ�����Č���B��

�D1 3�B(t��i)CMOS���_����IBISģ��

��1 ����Model_type��IBIS���Y(ji��)ģ�ͽM��

Model_type

[���b]

C_comp

[GND_ Clamp]

[Power_ Clamp]

[����]

[����]

V-T��

[�]

ݔ��

?

?

?

?

��

��

��

��

3�B(t��i)

?

?

?

?

?

?

?

?

I/O

?

?

?

?

?

?

?

?

�D1�@ʾ3�B(t��i)CMOS���_��IBISģ�ͽY(ji��)��(g��u)�����һ����������IBISģ���еĽM�����P(gu��n)�I��ȡ�Q��ģ����͡���1���Y(ji��)�˻����б�IBISģ�́��f��ģ�ͽM��Model_type�Q����

��(y��ng)��

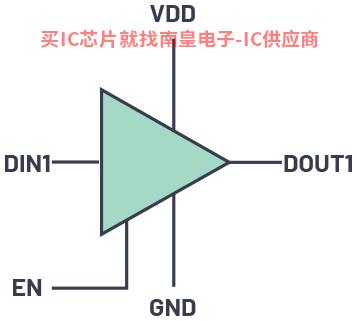

�ڱ����У��҂���ʹ�ü��O(sh��)ADxxxx������LTspiceģ�́턓(chu��ng)��IBISģ�͡�����һ����ݔ��͆�ݔ����(sh��)�־��_�����������_����ˣ��@��IBISģ�͌��Ѓɂ�ݔ�루DIN1��EN�������B(t��i)ݔ��(DOUT1)��

һ����f������IBISģ�����傀�������E��

�� �����A(y��)��ģ����

�� ����SPICE��ģ������ȡC_comp��V-I��V-T��(sh��)��(j��)�M(j��n)��LTspice���档

�� ��ʽ��IBIS�ļ���

�� ʹ��IBIS�������yԇ�z���ļ���

�� ���^IBISģ���cSPICEģ������ͬ���d�l���µ�ģ�M�Y(ji��)����

IBISģ���ṩ���͔�(sh��)��(j��)����С��(sh��)��(j��)�����(sh��)��(j��)������ͨ�^�����Դ��늉��������ضȺ�ˇ���_��[HA1]���˺�����Ҋ������ֻӑՓ���͗l����

Ibischk Golden Parserԓϵ�п����ڙz��IBISģ���Ƿ�һ��IBISҎ(gu��)����ibischk�Ɉ�(zh��)���ļ�IBIS.ORG���M(f��i)�@ȡ�W(w��ng)퓡����IJ��ü��ɡ�ibischk�ĵ�����IBISģ�;�ܛ����

�A(y��)��ģ����

���_ʼģ�M֮ǰ���Ñ���(y��ng)���d�O(sh��)��Ĕ�(sh��)��(j��)�փԲ����b��SPICEģ�ͺ�LTspice�ļ��������u������Ĕ�(sh��)�ֽӿڔ�(sh��)�������(��ݔ�롢й©�����B(t��i)��)��)ͨ�^�_�������

�����Դ늉��������ضȡ������·����(j��)�O(sh��)�䔵(sh��)��(j��)�փԴ_��(IC)���d�l�����b��͡��O(sh��)�����_���С���(sh��)��ݔ�����Ҏ(gu��)��RLoad��/��CLoad�����Լ����ƽݔ��늉��Ĕ�(sh��)��ݔ��(VINL)���ƽݔ��늉�(VINH)��ADxxx SPICE��2���г���ģ�͵�ָ��(bi��o)����(sh��)��

�����P(gu��n)���O(sh��)�䔵(sh��)�ֽӿڵ���Ϣͨ�^ʹ���P(gu��n)�I���ռ���һ��IBIS���ļ��С��P(gu��n)�I����IBIS���һ����������ģ��������̖�����Ę�(bi��o)�R����Ԕ��Ո��醱����֡�

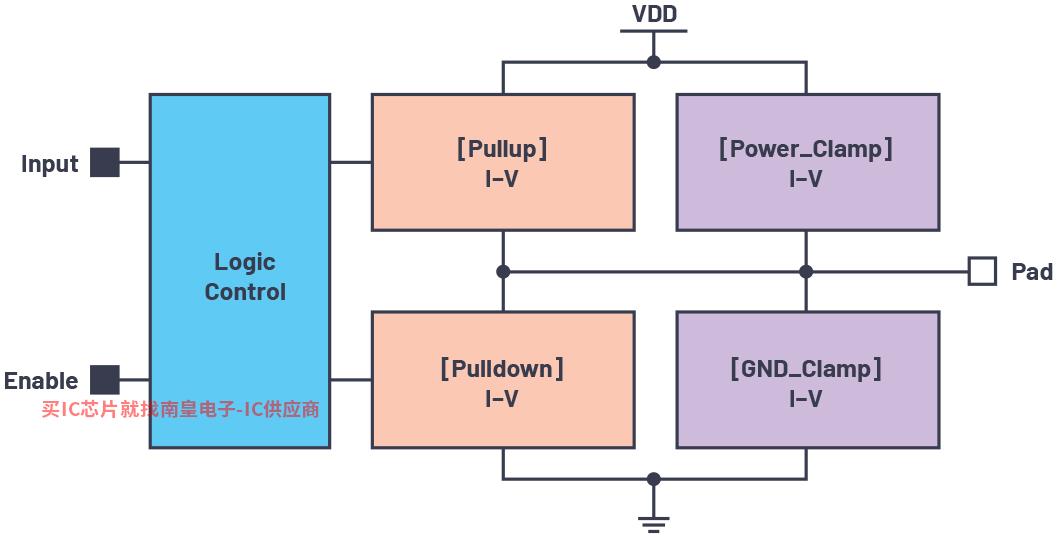

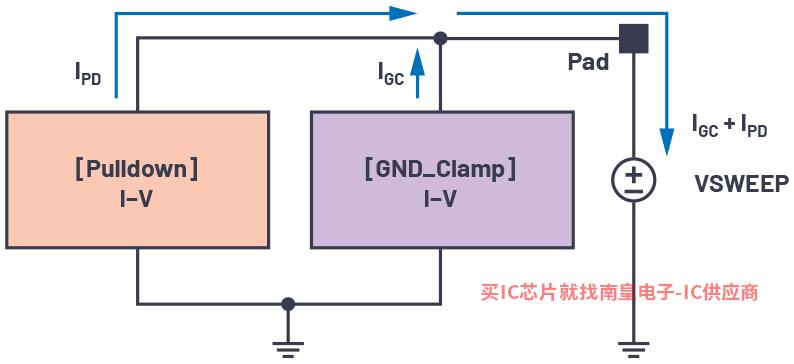

�D3 [Power_Clamp]��[GND_Clamp]�P(gu��n)�I�ֽY(ji��)��(g��u)����D

[GND_Clamp]��[Power_Clamp]�Ա�����ʽ�г�I-V��(sh��)��(j��)�@ʾ��(sh��)�־��_�����o늷��(ESD)�O(sh��)���О顣[Power_Clamp]��ʾ��VDD�����(zh��n)��ESD�ӵ�λ��ʾ���������w�О�GND�����(zh��n)��ESD�b�õ����w�О顣

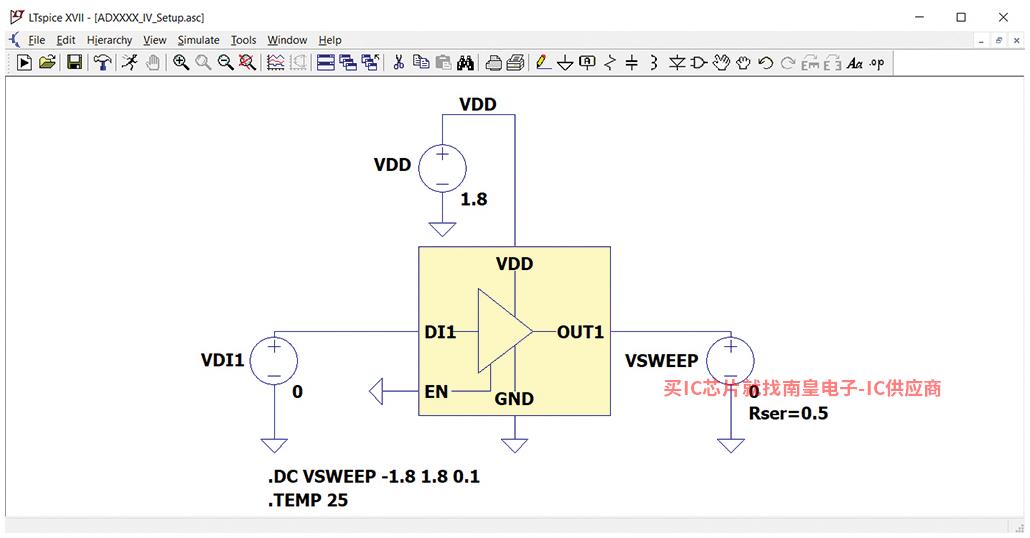

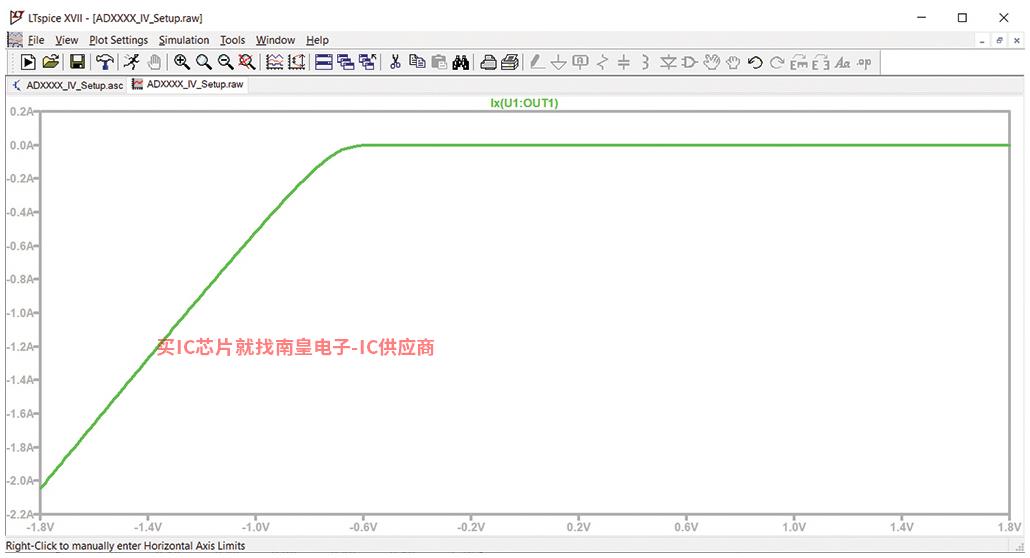

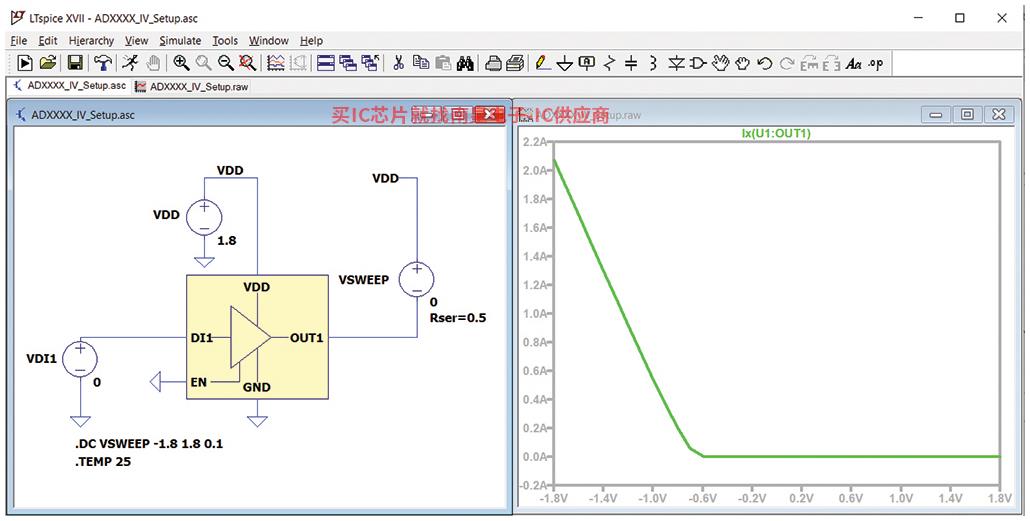

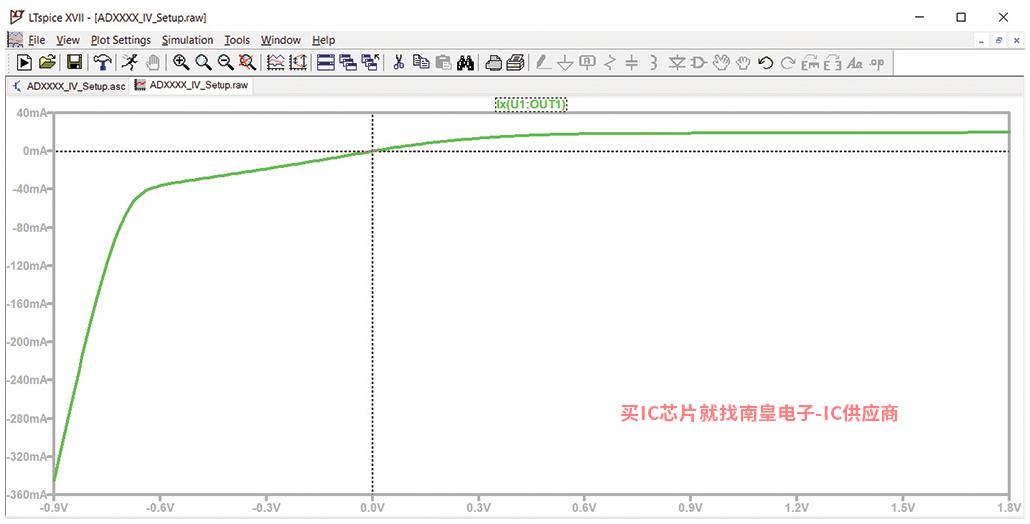

��LTspice�У�I-V��ʹ�Ô�(sh��)��(j��).DC SPICE�y������/ָ�DOUT�ÈD4��ʾ���O(sh��)�Üy��1�Ľӵ؊Aλ��ԓ�O(sh��)�ò����m��(d��ng)?sh��)��Դ늉���ԓ�O(sh��)�����Þ����ģʽ(Ҋ��5)�����Ա��CESD�O(sh��)���c�����·���x��VSWEEP����GND����(zh��n)����늉���ʹVSWEEP�_��ֻ�@ʾ����(zh��n)늉��ӵ�GND��λESD�O(sh��)������c(di��n)��

����(j��)IBIS��늉�܉�⣬Ҏ(gu��)��(y��ng)����(����Ǐ�-VDD��2 �� VDD����I-V�����Ĕ�(sh��)��(j��)�C1.8 V�� 3.6 V��ͨ�^ֱ�ӈ�(zh��)�д˲���������VDD�ⲿ늉������_�ԴλESD���������˱����@�N��r�������ǨC1.8 V�� 1.8 V������(n��i)����VSWEEP�������Ʒ���3.6 V��(sh��)��(j��)�c(di��n)���@�N�����m��������I-V��(sh��)��(j��)����

���⣬Ոע��һ��I-V��(sh��)��(j��)�����ֻ����100����(sh��)��(j��)�c(di��n)������(sh��)��(j��)�c(di��n)���^�˔�(sh��)���t��ibischk�ڷ������yԇ�Е���ʾ�e�`��.DC���������ʹ�õ��Ĕ�(sh��)��(j��)�c(di��n)С�ڻ����99���@�Ǟ����ݼ{2 �� VDD�~�┵(sh��)��(j��)�c(di��n)�����ơ�

ֱ������r��ģ�M�п��ܕ����F(xi��n)�dz���ķ�����������˽�Q�@�����}���Ľ��ƶ��O�܄݉��λ(-0.7 V)�O(sh��)�Þ�VDD ( 1.8 V)��Ȼ��(sh��)��(j��)���Ƶ�����Ҫ��CVDD��2 �� VDD I-V��(sh��)��(j��)����һ�N������ʹ��С���Rser�cVSWEEP���ƘO������Ĵ�(li��n)��

�D4 ADxxxx DOUT�ӵ��Qλ�O(sh��)��

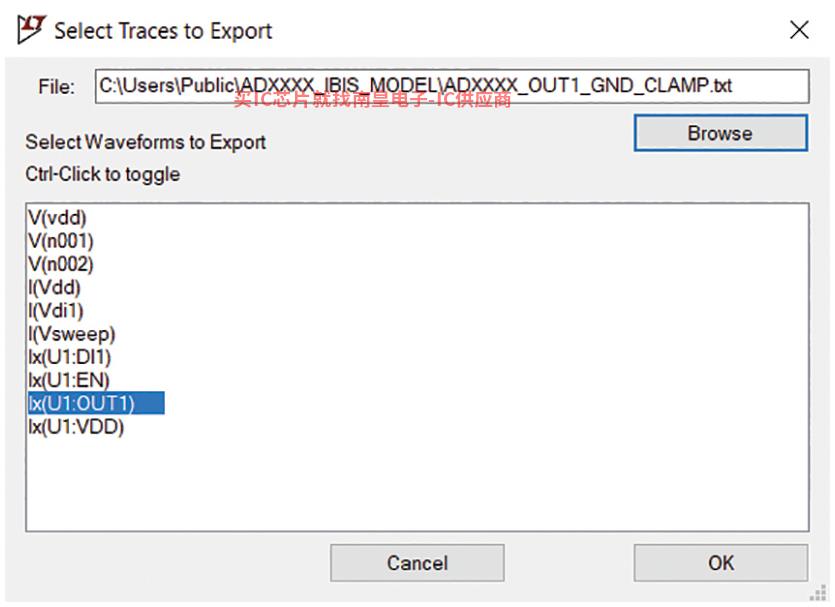

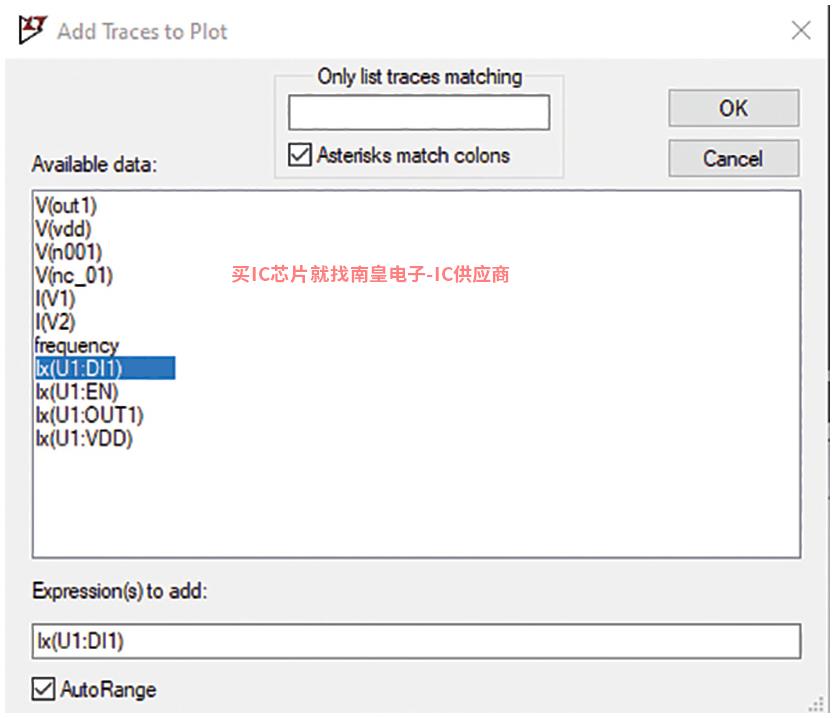

�Γ��������o��LTspiceģ�M�_ʼ�\(y��n)�С������u��DOUT����Ŀ��(bi��o)��(ji��)�c(di��n)��Ix(U1:DOUT1)���M�ļ��g(sh��)�Ƕȁ���I(VSWEEP)Ҳ�nj��ģ�����IBISģ����ҪIx(U1:DOUT1)����O�ԡ��@�Ǟ��˱M���p��I(VSWEEP)�M(j��n)һ����ʽ����(sh��)��(j��)��ʹ���m��ģ�͡��Y(ji��)����(y��ng)ԓ��ģ�M��ɺΓ��Y(ji��)�����ڱ��攵(sh��)��(j��)��Ȼ��Γ��ļ� -> ����(sh��)��(j��)��(d��o)�����ı�����(d��o)����Ҫ�����Ŀ䛣��Γ��ܜy��(ji��)�c(di��n)��Ȼ��Γ�OK������

�D5 �ӵ؊Aλ����Y(ji��)��

�D6 ��ģ�M��(sh��)��(j��)��(d��o)�����ı�

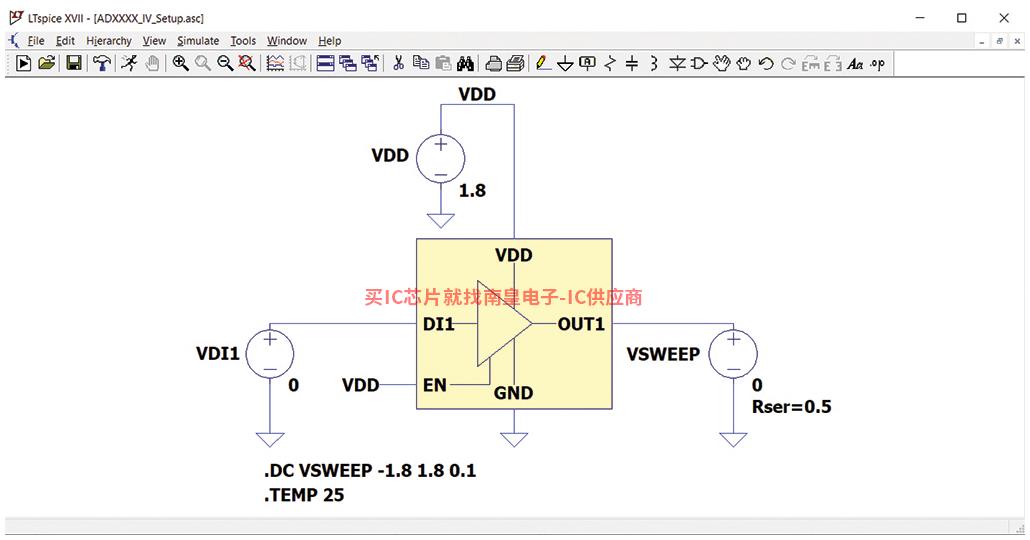

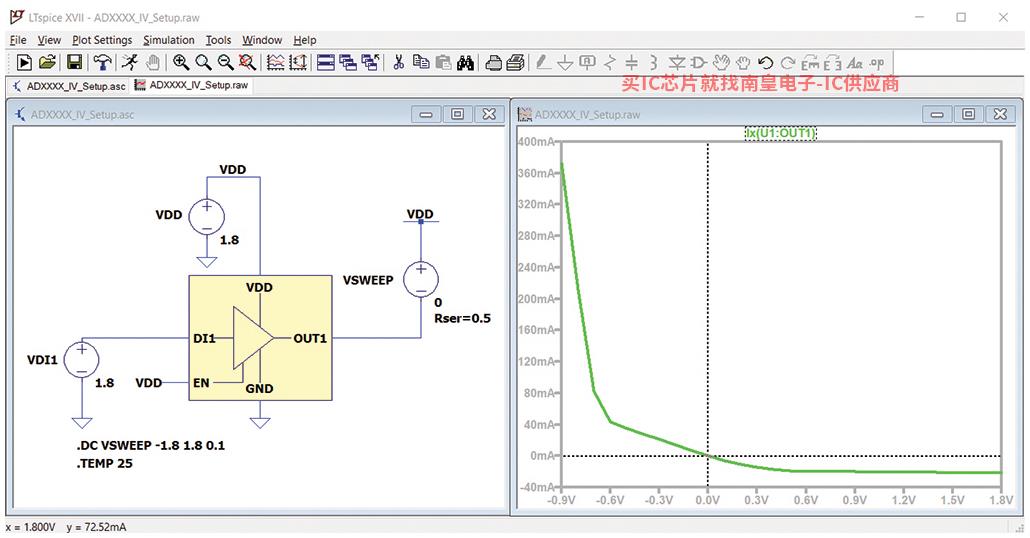

[Power_Clamp]��ˣ�����늉�����ڽӵ�λ���O(sh��)��VSWEEP��VDD�����(zh��n)���O(sh��)�úͽY(ji��)����

�D7 ADxxxx OUT�Դλ���O(sh��)�ü��Y(ji��)��

[����]��[����]

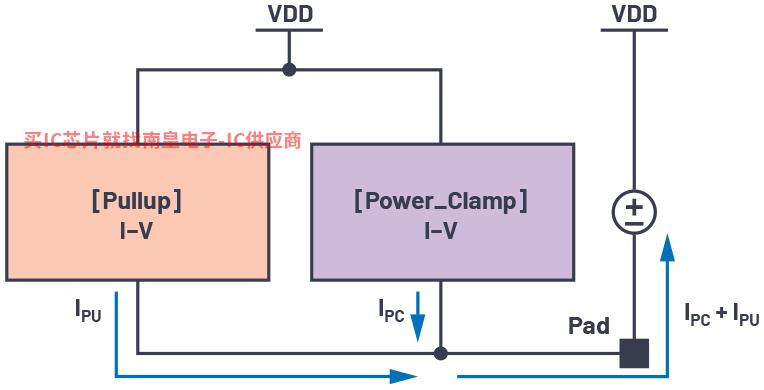

�D8 I-V�P(gu��n)�I�ֽY(ji��)��(g��u)����D

�D8�@ʾ��I-V�P(gu��n)�I�ֽY(ji��)��(g��u)����D��[����]��[����]��ʾ���_��������������Ԫ�ص��О顣�ԈD������ʽ��ʾ��������������MOSFET��I-V��������������ȡ[����]��[����]��(sh��)��(j��)�r���˽����ͨ�^�O(sh��)�����ֵ�����Ə�ݔ�����_ݔ������̖�Ƿdz���Ҫ�ġ��O(sh��)�ú���ȡ[����]��[����]��(sh��)��(j��)[GND_Clamp]��[Power_Clamp]��ƣ���DOUT���_ʹ�ܣ���̎�ڸ���ģʽ��

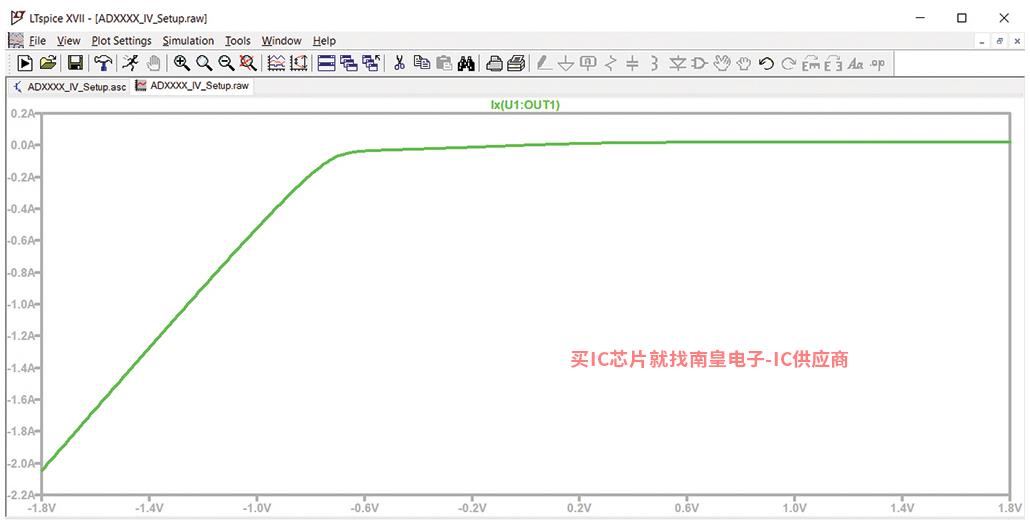

��ȡ[����]��(sh��)��(j��)��DOUT���_��(y��ng)�O(sh��)�Þ�߉0ݔ����0 V����ˣ�����O(sh��)���m��(d��ng)?sh��)��Դ늉���EN���_ʩ��1.8 V��Ч߉�߉���ʹ���܉�DOUT1���_����DIN߉0��0 V����DOUT���_�O(sh��)�Þ�߉0ݔ������ͨ�^��ֵ��(��5)�_�J(r��n)��

�D9 ADxxxx OUT1�����O(sh��)��

�D10 ADxxxx OUT1�����D

����ڷŴ�[����]��(sh��)��(j��)MOSFET��I-V������������

�D11 ADxxxx DOUT�����D(�s��ҕ�D)

����������(sh��)��(j��)�r��Ոע������(g��u)��[GND_Clamp]�Լ�[����]�Ŀ�������D12���Ը��õ��f���@һ�c(di��n)����Ҫ�h��[GND_Clamp]ֻ���[����]���攵(sh��)��(j��)���pȥ�M�����麆���˲�����[GND_Clamp]늉��������_ʼ늉��ͽY(ji��)��늉�����c[����]ֱ��������ͬ��

�D12 �������攵(sh��)��(j��)�Č�(sh��)�H���

�@ȡ������(sh��)��(j��)���O(sh��)�á��ṩ�m��(d��ng)?sh��)��Դ늉�DOUT1�O(sh��)�Þ�߉1 (1.8 V)���@���_������/���_����Ԫ����VSWEEPҲ�ڨC1.8 V�� 1.8 V�������܇����Լ�VDD���@�N��ʽ�B�Ӟ����(zh��n)��VSWEEP�����Է�ֹ�Ñ���ʽ����(sh��)��(j��)����Ҫ��IBISҎ(gu��)����

�D13 ADxxxx DOUT�����O(sh��)�ü��Y(ji��)��

��[����]һ�ӣ������[����]��(sh��)��(j��)����[Power_ Clamp]�Լ�[����]������ĽY(ji��)������ˣ��Ñ���Ҫ�ı����[����]��(sh��)��(j��)�Єh����(sh��)��(j��)[Power_Clamp]���������ֱ�����腢��(sh��)��ͬ���M����������ɡ����Ѵ�ң��������еĽM����I-Vʹ����ͬ��ֱ�����腢��(sh��)�M(j��n)�Д�(sh��)��(j��)�y����

�D14 �����[����]��(sh��)��(j��)��(sh��)�H���

[C_comp]

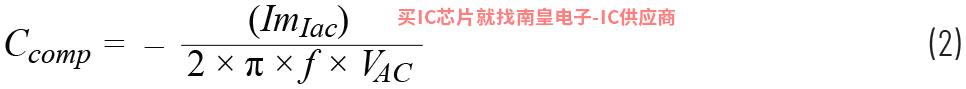

[C_comp]�P(gu��n)�I�ִ������_���������������С�����ͺ�����ֵ��ͬ�����Ǿ��w�ܺ���Ƭ�����������ͬ�ڰ��b�����������ͨ�^�ɷN��ʽ��ȡ[C_comp]����(d��ng)���_�ɽ���늉���늕r������1�еĹ�ʽ��2�еĹ�ʽ�����Á�Ӌ�㡣

����

PLX������ ImIac�����y�����ֵ̓

�� F�������Դ���l��

�� VAC�������Դ�ķ���

ʹ��LTspice�M(j��n)��C_Comp��ȡ

�����_�������ݿ���ͨ�^�ṩ����늉����l�ʒ������ȡ�������ṩ�˽���늉��������Ҫ�y������Č�(sh��)�H��̓�M���֡���(d��ng)ʹ�ý���늉���늕r����횷��D(zhu��n)����ĘO�ԁ�y�����_����ݔ�����ֵ���y��ݔ�����_����ݕr���D15��ʾ��Ψһ׃���nj������Դ�B�ӵ�ݔ�����_��

�D15 ADxxxx C_comp��ȡ�O(sh��)��

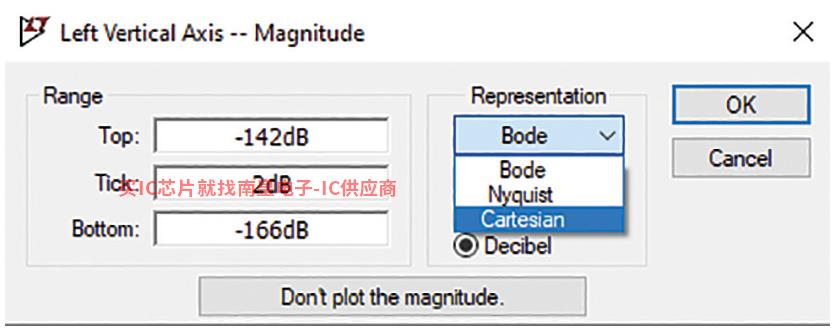

����늉������ֵ����������ֵ����ͨ���O(sh��)�Þ�1 V����������SPICE�l�ʒ���ָ�ʹ��.AC��(d��ng)�����L�Ʋ��Εr��Ĭ�J(r��n)�O(sh��)�Þ��Բ���ģʽ�@ʾ����λ��dB�����ֵ����O(sh��)�Þ�ѿ���ģʽ���Ա㾏�_����ݹ�ʽ����ֱ��̎����Ҫ�z�龏�_������ݲ��Σ��Ñ���������I�Γ����δ��ڣ�Ȼ��Γ����Ӳ�����Ȼ���x��y�������_���ɗl�����@ʾ�ڲ��ΈD���ڡ�

��(sh��)����ʾ���y����Č�(sh��)����̓����ʾ���y�����̓����

�D16 ��D�����Ӿ�·��Ԓ��

���D���O(sh��)�ÏIJ��ظĞ�ѿ��������I�Γ����δ������(c��)��y�S�����_��v�S-�����Ԓ��Ȼ�D�ΏIJ��ظĞ�ѿ�����

�D17 ���D�O(sh��)�ÏIJ��ص��ѿ���

- ������ӹ���0.56��2�|����ISOCELL HP3�D�������

- Ӣ�w���cOxford Ionics�y���_�l(f��)���M(j��n)���x����������̎����

- ͬ�r��(sh��)�F(xi��n)�ИI(y��)���췴��֏�(f��)�r�g�ͳ��͌�(d��o)��� 600V�͉������Y(ji��) MOSFET ��R60xxVNxϵ�С� ~�������I(y��)�O(sh��)��Ͱ�ɫ

- ����������_�P(gu��n)�Դ����Ҫ�ԣ�

- Ӣ�ؠ��J�ŵĴ_�J(r��n)���r��֧�ֲɵV

- Diodes��˾��32ͨ��PCIe 3.0����ГQ��֧���ȳ��Ͷ����C(j��)�B�ӹ���

- ��˹��������������214�|��Ԫ ������32.9�|��Ԫͬ�ȷ���

- ��(li��n)�W(w��ng)��ȫ:��(sh��)�F(xi��n)ȫ��ɳ��m(x��)��

- 3��23�գ��������e��оƬ �C�� Ӣ�ؠ�������CEO����ϯ

- ��˹��CEO�����uEUV���Ї�����������x��

- �Q(m��o)�ɂ�؛Laird Connectivity Sentrius IG60-BL654 BT610���T��

- ����GPU���RGTX1050�����a(ch��n)GPU�������������1.25�|Ԫ ��a(ch��n)Ʒ���u