оƬ��ُ�W��ע�����χ������ڙ�IC�����̬F(xi��n)؛�YԴ��оƬ��挍�r��ԃ���ИI(y��)�r���������ُ����ICоƬ�����Ȍ��I(y��)оƬ��ُƽ�_��

ժҪ

�S��Խ��Խ����O��ּ�ڽ�Q�F(xi��n)���㷨���ٹ���ؓ�ɣ��ߎ�������������܉���Ч���Ƅӵ����ٽ���������O��֮�g��Achronix��Speedster7t����FPGAоƬ���Լ����µġ��߶Ȅ�(chu��ng)�µĶ��SоƬ�ϾW(2D NoC��̎���@Щ�ߎ�����������Achronix��FPGA�����е�2D NoC���F(xi��n)����߉�YԴ���F(xi��n)2��һ�N��(chu��ng)��D NoC�c���y(t��ng)������ȣ�����Щ��(chu��ng)�º̓rֵ������Ƥ��ӑՓ���@�ɷN���F(xi��n)D NoCԓ������չʾ��ܛ2�ṩ��ʾ���OӋD NoC���F(xi��n)��ȣ�Achronix 2D NoC���������ܣ��p����e���s���OӋ�r�g��

��B

Achronix����Speedster7tϵ��FPGAͨ�^���Ʉ�(chu��ng)�£���ȫ�����OӋ��Ƭ��ͨ�żܘ�D NoC�m���ߎ�������������Ҫ����ԓFPGA�O��������@2D NoC�B�ӵ����и��ٽӿڣ���������400G��̫�W��PCIe Gen5��GDDR6��DDR4/5�˿ڡ���ԓFPGA�ڿɾ���߉����ϲ�����һϵ�и����к���ͨ�����քe��FPGA�W�j�����ֲ��ڿɾ���߉��е�ˮƽ�ʹ�ֱ�����ϡ������@Щ�к��У���NoCÿһ�к�ÿһ�н����λ���Լ��l(f��)���c��Ŀ��NoC�L����(ji��)�c��NAP�����@ЩNAP�䮔NoC�YԴ��Ŀ�ĵ�λ�ڿɾ���߉����С�

���ˌ�Achronix FPGA�Ѓ��õ�2D NoC���ɾ���߉�����ʹ�Â��y(t��ng)������(chu��ng)����NoC��ˣ��҂��u���ˎNܛ��NoC�OӋ�������ͬ���u����FPGA����ֲ�Y�����҂��x�������m�����WԺ��ܛ2D NoC��https://github.com/agalimberti/NoCRouter��2017���OӋ���@�NܛNoC����W�j��mesh���x��ǰհ���A�y�ГQ�ѽ����F(xi��n)���@�NܛNoC����W�j��mesh���x���A�y�ГQ�ѽ����F(xi��n)���ڌ�ʩ�^���У�����Ҫÿһ��mesh�惦���D�l(f��)�����Ɔ�Ԫ��(ji��)�c�ϵĶ����惦����flit����

����Ƭ��2D NoC���F(xi��n)ģʽ�cʹ��߉����YԴ��ܛ���F(xi��n)ģʽ֮�g�IJ���Ȅ�(chu��ng)����һ������AlexNet 2D���e��19�������OӋ��Ȼ����������2��D NoC�OӋ���^��������Ҫָ�ˣ������YԴ���OӋ����Jorjin�����Լ��OӋ�r�g���OӋ�r�g���ڹ����о��g�OӋ�r�g�����Y�������������N��r�¼���Achronix 2D NoC�������@��(y��u)��ܛ���F(xi��n)��

2D NoC�p���YԴ��ʹ��

���˱��^�ɷN��ͬ��2�ND NoC�OӋ���ɷN2D NoC���c�F(xi��n)�е�2D���e��conv2d���Y���OӋ��conv2d�OӋ��(zh��)��ݔ��D��AlexNet 2D���e����conv2d�OӋ��Ҫһ�ɂ�AXI-4�B��:һ�������xȡ�ȴ棬һ�����ڌ���ȴ����AXI-�Ĉ�(zh��)���x�������F(xi��n)��ܛNoC�x�����������Ѽ���AXI-4�ӿڣ�conv2dÿ��ģ�K������mesh��(ji��)�c��Ȼ��ܛNoC������GDDR�惦�ӿڵĔ�����ںͳ���-ܛNoC���g���ȴ�ӿ��B�ӵ���20��mesh��(ji��)�c������ʽNoC�@�N�B���ѽ����������g����GDDR6��ÿ��conv2d�Ĺ�(ji��)�c����(ji��)�c���й�(ji��)�cͨ�ţ�����conv2d��(ji��)�c֮�g�]��ͨ�š�

Achronix 2D NoC���OӋ����(ji��)

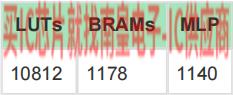

ԓ�OӋ��19��conv2d�L��ģ�K�������L��ÿ������GDDR6�惦������20�������ǿ��e�ģ����GDDR6�ӿ�ֱ���B�ӵ�����2D NoC��80�����õ�NoC�����c��NAP������38�������B��conv2d������ÿ��conv2d����ʹ��64�_�C���W��̎������MLP�������ڴ�ֱ�����ϸ��w�ɂ�NAP������@��������ᘌ�����2��D NoC�����Բ����pAXI-4�����B��conv2dģ�K���±��г��˱��OӋ��ʹ�õ��YԴ��

��1 Achronix 2D NoCʹ�õ��YԴ

�D5 Achronix��2D NoC��NAP

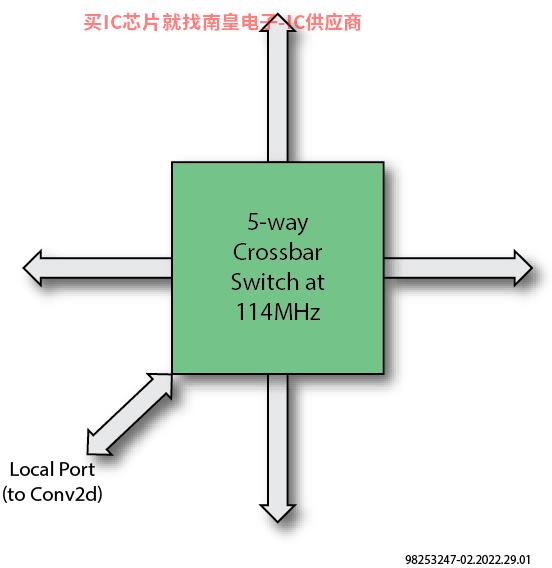

ܛ2D NoCʹ����·�����_�P��crossbar switch����һ���˿ںͱ���conv2d����ͨ�ţ������˿��c�W���е���һ����(ji��)�cͨ�š���(ji��)�c����(ji��)�c�B�ӵ��l�ʞ�82 MHz���Ķ���һ����(ji��)�c���γ���ߵ�21 Gbps��GDDR6�ӿڎ���������Ŀ�D�@ʾ��ܛ2D NoC mesh���g�Ľ����_�P��

- ˼����������ϯ2022���Ϻ�ȫ��Ͷ�Y���M�������ȫ���@�^(q��)�Ŀ���s

- ��ȥ�M��֮�s �_���f���Ԅӻ��c���B(t��i)�������һ�����Iδ�픵��

- �P��Ԫ��������˼��

- �ȸ��_�l(f��)ƹ����C���� ���B�m(x��)��340�Σ�

- ����϶(WBG)�댧�w: �ɿ��Ĺ�(ji��)�ܽ��Ľ�Q����

- TrendForce����һ���Ⱦ��A�����aֵ�����L8.2%

- ��I(y��)�����I(y��)��(li��n)�Wƽ�_ƽ�_ �I܊�߫@������-������I(y��)ƪ(1)

- �����ưl(f��)���Ɣ�������̎���� CIPU������� CPU

- (li��n)�l(f��)��Q3�I�չ�Ӌ���p1~9% ȫ��չ��׃������

- Ӣ�ؠ�朽Ӯa�I(y��)���˲�FPGA���B(y��ng)�Ї���(chu��ng)�����ĵĄ�(chu��ng)���˲�

- ��2021���Ї���ƽ�_�����Ʒ����Ј����~�����l(f��)��

- ��һ��������һ�����b�еĹ���������ⷨ�댧�wGaN���w��